## **AND8487/D**

# Asynchronous Drive Guidelines for the NIMD6001 Dual N-Channel Switch

ON

ON Semiconductor®

http://onsemi.com

APPLICATION NOTE

Prepared by: Robert Maigret ON Semiconductor

#### Introduction

The NIMD6001 is a dual low-side N-channel switch with common diagnostic and disable functions. When both switches are driven synchronously (identical signal applied to both gate terminals), and the two Source pins are interconnected, the permissible maximum applied gate pin voltage is constrained only by the internal ESD protection diodes. When driven asynchronously, however, channel-to-channel crosstalk becomes a consideration. If one switch is turned on while the other is off, the latter can be impacted by currents that flow in the internal common disable circuit. Limiting the maximum turn-on gate pin voltage to values specified in this Application Note will prevent undesirable interaction between the switches.

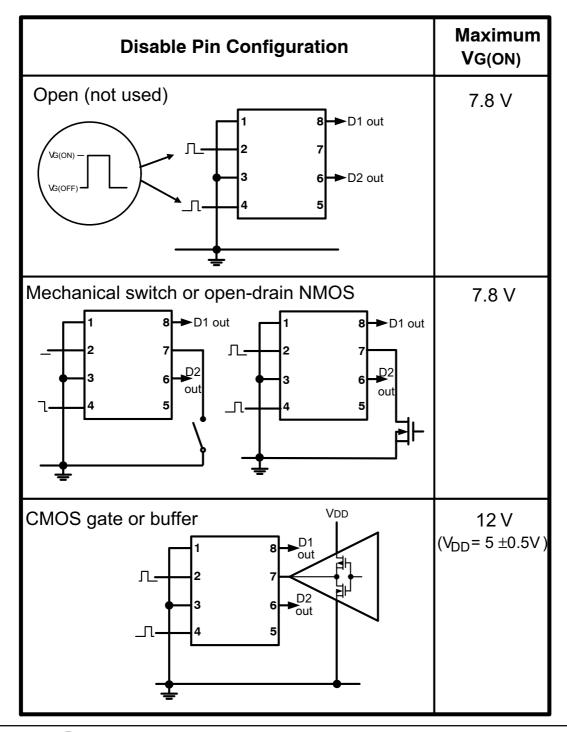

The most common Disable pin configurations are:

open (disable function unused);

**mechanical switch to common** (close to turn off both switches);

**NMOS open drain** (active low to turn off both switches);

CMOS gate or buffer sink-source output (active-low to turn off both switches).

The recommended maximum turn-on gate pin voltage is dependent on which of these configurations applies. Note also, in some configurations, the actual internal peak gate-source voltage may be less than the voltage applied to the gate pins.

| Disable pin configuration                | Recommended maximum gate pin turn-on voltage (VG max) | Actual Vgs with (VG = VG max) and opposite gate pin connected to Source 1 and Source 2. |

|------------------------------------------|-------------------------------------------------------|-----------------------------------------------------------------------------------------|

| Open                                     | 7.8 V                                                 | 7.0 V                                                                                   |

| Mechanical switch to common              | 7.8 V                                                 | 7.0 V                                                                                   |

| NMOS open drain                          | 7.8 V                                                 | 7.0 V                                                                                   |

| CMOS gate or inverter sink-source output | 12 V                                                  | 5.7 V<br>(Note 1)                                                                       |

<sup>1.</sup> CMOS V<sub>DD</sub> = 5.0 V.

<sup>2.</sup> Operating voltage applied to Pin 7 (*Disable*), relative to Pins 1 and/or 3, should not exceed 7.5V. Higher voltage may cause an increase in off-state Drain currents.

ON Semiconductor and are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

### **PUBLICATION ORDERING INFORMATION**

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor P.O. Box 5163, Denver, Colorado 80217 USA Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com N. American Technical Support: 800-282-9855 Toll Free USA/Canada

Europe, Middle East and Africa Technical Support: Phone: 421 33 790 2910 Japan Customer Focus Center Phone: 81-3-5773-3850 ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative